views

Recently, according to eenews, Samsung’s foundry has taped out 3nm chips based on a gate-all-around (GAA) transistor architecture. By using nanosheets, they have manufactured MBCFETs (multi-bridge channel field effect transistors), which can significantly enhance transistor performance. Mainly replace FinFET transistor technology.

This process requires a set of design and certification tools different from the FinFET transistor structure, so Samsung uses Synopsys' Fusion Design Platform. The physical design kit (PDK) for this process was released in May 2019 and passed the certification last year. With this successful tapeout, it means that the time for large-scale mass production of Samsung's 3nm chips has officially approached.

Charlie Bae, Samsung's executive vice president and director of foundry sales and marketing, said: "The next-generation process node (3nm) based on the GAA structure will enable Samsung to take the lead in opening a new smart connected world while strengthening our technological leadership."

What is GGA?

GGA-(Gate all around Field Effect Transistors, GAAFET), also known as full-circle gate transistors, is an emerging technology that continues the existing semiconductor technology route, which can further enhance the gate control ability and overcome the physical scaling of the current technology And performance limitations.

It is understood that GAAFET has two structures, one is a common GAAFET that uses nanowires as electronic transistor fins, and the other is a multi-bridge channel field with thicker fins in the form of nanosheets. The effect tube MBCFET, these two ways can realize 3nm, but depend on the concrete design. From GAAFET to MBCFET, it can be seen as a leap from two-dimensional to three-dimensional, which can improve circuit control and reduce leakage rate.

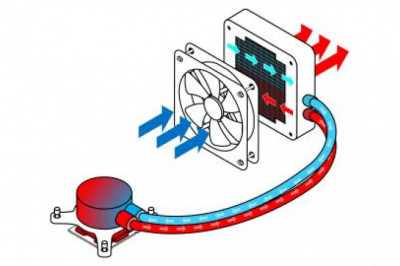

According to experts: GAA transistors can provide better electrostatic characteristics than FinFETs and can meet certain gate width requirements. This is mainly reflected in the enhanced GAA channel control ability under the same size structure, which makes it possible to further reduce the size; the traditional FinFET channel is only surrounded by the gate on three sides, while GAA takes the nanowire channel design as an example. The entire outer contour is completely wrapped by the gate, which means that the gate has better control performance on the channel.

Sylvain Barraud, a senior integration engineer at Leti, pointed out: "Compared with FinFET, in addition to having better gate control capabilities, GAA stacked nanowires also have a higher effective channel width and can provide higher performance."

According to Samsung, compared with the 7nm FinFET manufacturing process, the logic area efficiency of 3nm GAA technology is increased by more than 35%, power consumption is reduced by 50%, and the logic area is reduced by 45%.

It can be seen that the GAA transistor structure marks a key turning point in process technology, which is essential for maintaining the scaling trajectory required for the next wave of ultra-large-scale innovation.

FinFET has come to an end?

In the past ten years, FinFET technology has successfully continued Moore's Law, but today, with Moore's Law stalling, FinFET seems to have come to an end.

Speaking of FinFETs, we have to start with planar MOSFETs. Since the birth of planar MOSFET device technology, the feature size has been shrinking continuously as guided by Moore's Law. In the process of reducing the feature size of transistors, although various difficulties have been encountered, by changing the aluminum interconnection to the copper interconnection, adding High-k materials to the gate, and introducing stress engineering, methods such as the introduction of stress engineering can all be used without changing the planar device process. In the case of making the size smaller.

But when the gate length approaches the 20nm threshold, the ability to control current drops sharply, and the leakage rate is also increasing. The traditional planar MOSFET seems to have come to an end, and changes in materials cannot solve the problem.

In this regard, Professor Hu Zhengming of the University of California at Berkeley gave a new design, that is, FinFET transistors, also known as fin field effect transistors. In FinFET, the channel is no longer a two-dimensional, but a three-dimensional "Fin" shape, and the gate is a three-dimensional surrounding the "Fin", which greatly increases the gate's ability to control the channel , So as to solve the leakage problem.

Professor Hu Zhengming formally put forward the FinFET solution in the academic circle in 2001, but it will be implemented only ten years later. Intel took the lead in the FinFET process and launched the commercialized 22nm FinFET process technology in 2011. Subsequently, major semiconductor manufacturers around the world, including TSMC, actively followed up and gradually moved into the FinFET process. Starting from 16/14nm, FinFET has become the mainstream choice for semiconductor devices, successfully promoting the development of several generations of semiconductor processes from 22nm to 5nm, and will expand to the 3nm process node.

Write at the end

3nm is about to happen, and so will 2nm. Since there is no single technology that can meet all applications, in the process of chip shrinking and function expansion, process progress, transistor structure changes, and other methods will alternate, continuously pushing chip performance upward.

Under this circumstance, in addition to the need for manufacturers to show their own abilities, how to obtain the largest niche from technology, market and cost will be the key to competition among enterprises. In particular, the cost of advanced semiconductor manufacturing is very high. If a better balance between production technology and manufacturing costs is not achieved, future development will also be very difficult. Considering the huge involvement system of the semiconductor manufacturing supply chain, not only the manufacturing equipment, but also the design tools, inspection and testing, etc., if there is no excellent solution, it will be difficult to maintain an advantageous position in the competition.

When writing this text, another message came from the front: “Samsung has carried out a lot of marketing and hype around the 3nm node. The current situation seems to be severe, and the product performance seems to have undergone a lot of changes. The 3nm node based on the GAA architecture is expected to be Postponed until 2024..."

It is not difficult to foresee that the era of GAA transistors is beginning.